流片前嵌入式系统评估

使用专门设计的风险评估工具辅助安全评估

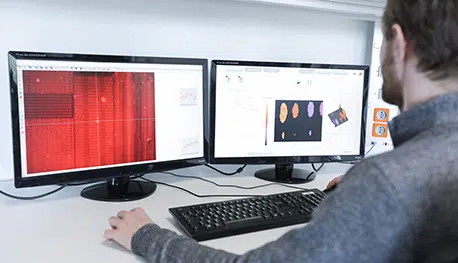

Secure-IC使用电子设计自动化(EDA工具)软件,验证产品在RTL级、逻辑综合Post Synthesis级和布局布线级等所有设计级别的安全。评估在理想条件下进行,通过模拟再现最佳攻击模式,不会受到噪声或测量偏差影响。

Secure-IC使用电子设计自动化(EDA工具)软件,验证产品在RTL级、Post Synthesis级和布局布线级等所有设计级别的安全。评估在理想条件下进行,通过模拟再现最佳攻击模式,不会受到噪声或测量偏差影响。

使用VirtualyzrTM进行流片前评估

- 从设计上保障安全

- 提供一个安全验证层,与功能验证流程协同工作

- 允许在不同的设计级别执行安全检查点。该功能可用于非回归测试。

- 检测设计中的安全漏洞并确定其特征

- 将漏洞与设计对应起来,帮助设计人员定位和解决潜在的问题。

- 由于不需要测量设备或平台,评估成本较低。

- 评估混合设计(硬件和软件)

流片前评估的三个步骤

第1步

根据概念设计级别(RTL级/Post Synthesis /Place & Route)进行设计的模拟。取得模拟痕迹后,用户可以选择要使用VirtualyzrTM评估的设计部分。

- 第2步

采用数学消耗模型对模拟痕迹进行研究和处理。

- 第3步

基于所取得的泄露痕迹进行高级物理分析。接下来可进行接下来可进行侧信道攻击(side-channel attacks)和故障注入攻击(side-channel attacks)分析。

确保设计生命周期各个阶段的安全

VirtualyzrTM 工具是LaboryzrTM解决方案的一部分,专门用于帮助公司确保设计生命周期各个阶段的安全。

Secure-IC提供的工具可用于检测硬件木马,也可用于对设备进行黑盒分析。

Secure-IC还可以提供安全评估和渗透测试服务。

第1步

第1步